多核与PD的技术分析 | |

|---|---|

| http://www.sina.com.cn 2006年11月07日 09:31 太平洋电脑网 | |

|

作者:夜夜 四核处理器的推出无疑是肯定了多核处理器的发展方向,就在一年前Pentium D的推出,不少朋友就对此表示不太关注,认为双核处理器很可能是一个噱头,并非是一个“现实”的产品。其实不然,今年双核处理器价格大降后,其市场占有率已经大大提高,不少厂商将2006年比喻为双核年,而明年将会是双核大规模占领市场的重要的一年。 现在推出的四核产品,它又将在市场上扮演什么样的角色呢?在专题里我们看到了不少关于四核的资料了,本文章着重点放在四核与此前发布的Pentium D产品的比较上。因为两者的组合方式有点类似,都是用两个核心“集结”在一起的方式,此前真假双核风波也与此有着一定的关系。 双核心Pentium D处理器 在推出双核心产品之前,无论是进行视频编缉、运行大型3D游戏、还是需要同时运行多个程序,都对计算机的性能提出了较高的要求。单核心产品就算拥有很高的频率,但是当开启多任务程序后,延迟等待或画面滞留等现象已经无法为人忍受。为了使用户享受到更出色的流畅度,Intel推出了包括双核心Pentium D处理器在内的众多Pentium处理器。 Intel Pentium D双核心处理器恰好可以满足这些要求。Pentium D双核心处理器共推出了三种不同规格的产品,主频分别为3.2GHz、3.0GHz和2.8GHz。双核心处理器能为用户提供额外的运算资源,从而大幅度提高了PC的工作效率。对于那些具有高强度任务和多线程运算需求的用户来说,双核心处理器能为他们带来全新的使用体验。 Pentium D是在一颗处理器中集成了两个完整而独立的处理核心,并在相同的频率下同时运行。两个处理核心在共享芯片组存储界面的同时,可以完全独立的完成各自的工作。同样针对的是多线程应用环境,也许你会问,究竟双核技术与超线程技术区别何在?这个问题很简单,二者本质的区别就在于超线程技术只是通过模拟逻辑双核来实现对多线程处理的性能改善,而双核心技术则是直接通过物理双核来提升处理器的多线程运算能力。借助双核技术,用户甚至可以在同一台PC上同时满足不同用户的需求,例如借助家庭网络环境,使每个家庭成员都可以利用同一台配置了双核处理器的PC来干自己想干的事,比如游戏、听音乐、录制电视节目等,而这些高强度的应用叠加在一起,也丝毫不会影响单一的使用感受。简单的说,双核技术就是HT超线程技术的一次质变和革命。 双核处理器的一些新技术 Intel增强型Speedstep技术:Pentium D 830和840处理器都支持增强型Speedstep技术。这种创新技术可以动态调整处理器的电压和核心频率,从而减小平均能耗和发热,也从很大程度上缓和散热设备的压力。功耗和热量的降低不仅可以降低主机在运行中所产生的噪音,工程师们也可以利用散热方面的优势设计出更小巧的部件。在与现有的节能特性结合的基础上,增强型Speedstep技术能很好权衡PC的能耗需求,从而在用户需要的时候提供强劲动力,在PC闲置的时候充分节省资源和减小电力消耗。 一级缓存:Pentium D处理器提供了两个16KB的数据缓存,除此之外,每个处理核心都包含一个Execution Trace Cache(跟踪执行缓存),可以根据运行程序的顺序存储12KB大小的解码微指令。这种做法可以很大程度上提高缓存的利用效率,从而进一步改善系统性能。 2MB 二级高速缓存:基于90纳米制程的Pentium D处理器为每个处理核心配备了1MB的二级高速缓存,总容量为2MB,从而让系统能更快捷的对更多常用数据进行访问。 Intel EM64T:对于Intel的32位架构来说,EM64T技术通过允许处理器访问更多容量的内存来增强原有的系统性能。 Execute Disable Bit:该特性需要特殊 操作系统支持,可以将内存标示为“可执行”和“不可执行”两类,如果试图利用不可执行内存运行代码,处理器就会对操作系统发出错误提示。Pentium D上市后,Pentium 4 6XX系列和5XX系列处理器所处的主流市场最为兴盛,同时也是竞争最为激烈的。由于主流市场的受众范围最广,因此产品线也最为丰富,无论6XX系列还是5XX系列的处理器都分别拥有多种不同规格型号的产品,对于Intel的处理器命名规格不甚了解的用户来说,他们甚至很难从不同CPU的名字中区分出他们的之间的规格差异。 简单的说,6系列处理器是主流市场中定位稍高的一类产品。该系列中全线处理器主频从3.0GHz到3.8GHz不等,均为90纳米制程,拥有2MB的二级高速缓存和800MHz的前端总线。在对各项Intel专利技术的支持上,6系列处理器也做得十分到位,全线产品都支持超线程技术、EM64T、病毒防护技术和增强型Speedstep技术。6系列面向的是主流市场中需求较高的用户群。 相对6系列处理器而言,5系列处理器的规格就更加繁多了,不过在了解了他们的命名规则后,你也可以很容易区分不同CPU之间的规格差异。5系列处理器的主频从2.8GHz到3.8GHz不等,均为90纳米制程,拥有1MB的二级高速缓存和800MHz的前端总线。而在对各项Intel专利技术的支持上,不同型号的CPU情况就不一样了。简而言之,所有5系处理器均支持HT超线程技术,但不支持增强型Speedstep技术;名为Pentium 4 5X0或5X3的处理器对EM64T和病毒防护技术都不提供支持;名为Pentium 4 5X0J或5X3J的处理器仅支持病毒防护技术;而名称为Pentium 4 5X1或5X6的处理器则同时支持EM64T和病毒防护技术。由此可见,Pentium 4 5X1或5X6系列处理器在主流市场中的定位居中,而5系列处理器相对同等频率的5X1处理器而言,定位则要偏低一些,因为他们支持的Intel专利技术相应较少。 双Core(四核)处理器

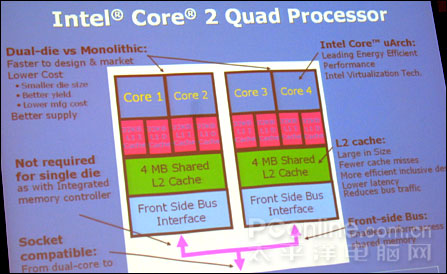

目前发布的四核产品是采用了类似以前Pentium D所采用的方案,就是把Dual—die放在一起,两个酷睿2核心整合在一起就能很快地设计出新的四核产品。对于厂商来说,这样的好处是可以让四核很快地面世,而它的并行处理能力提高幅度也是令人满意的。 由于四核产品采用的是酷睿2微体系架构,所以其核心创新功能与酷睿2是一样的。 Core构架的每个环节都比过去的CPU更大更宽,它的向量和标量执行单元要比过去的Netburst构架大的多。更多更大似乎成为了Core设计组的核心思想-更大的DL解码逻辑电路、更大的RBS重排序缓存、更大的RS预留缓存、更大的数据输出口,更多的晶体管、更多的缓存,INTEL把一系列强大的硬件条件集合在了Core一体。 Core拥有一系列方法来解决ILP限制的问题,在数据前期处理方面有宏指令融合(Macro-Fusion)、微指令融合(Micro-ops Fusion)、分支预测单元(Branch Prediction Unit)等来保证编码快速送入到正确的执行单元,而在数据输出端则有主够的指令输出窗口(Instruction Window)来有序的分配每个流水线的任务,INTEL还特别提到他们已经改进了SSE指令中的一个重要缺陷,可以极大提高效率,以上这些多方面的全面改进使得Core的运算能力要比过去Netburst构架的CPU强大的多。 为配合Core增多的32条预留缓存空间(Reservation Station),Core的执行核心(Execution Core)也拥有了重新设计的数据输出端口(Issue Port) ,相比P6的5个端口及Netburst的4个端口,Core拥有了6个数据输出端口。其中3个端口专门负责指令执行单元,这将更好的满足现时CPU的巨大数据传输需要。 Core拥有3个64-bit整数执行单元(Integer Execution Units),每个单元可以独立处理一条64-bit整数数据,这样Core就有了一套64-bit的CIU复杂整数单元(Complex Integer Unit),这和P6构架相同。然后Core另外有2个SIU简单整数处理单元(Simple Integer Units)来快速运算较简单的任务,其中一个SIU将和分支执行单元BEU来共同完成部分的宏指令融合micro-ops fusion。上图中斜体字的部分尚未确定 对于INTEL的X86 CPU来说,这是首次可以在一周期内完成一阶64-bit的整数运算,这使Core已经走到了IBM PowerPC 970的前面-PowerPC 970需要有2个周期的延迟。另外,因为3个IEU整数执行核心使用了各自独立的PORT数据出口,所以整个Core处理器可以在一周期内同时执行3组64-bit的整数运算。 有着如此强大的整数处理单元,Core在性能上将比现有Pentium 4快的多,它在移动平台、服务器、3D图形上4倍于Pentium 4的性能表现将使全世界对INTEL CPU眼目一新。 Core的浮点执行单元 Floating-point execution units Core构架拥有2个浮点执行单元(Floating-Point Execution Units)同时处理向量和标量的浮点数据,位于PORT 1的FPEU-1浮点执行单元负责加减等简单的处理,而PORT 2的FPEU-2浮点执行单元则负责乘除等运算,这样在Core中就将FADD/VFADD和FMUL/VFMUL划分为两组,使其具备了在一周期中完成两条浮点指令的能力。

Core的流水线 INTEL还不能透露Core具体的流水线详情,目前我们只能告知Core采用14条流水线-这和 PowerPC 970是一样的,而之前的Pentium 4 Prescott拥有30条,P6构架为12条。短的流水线意味着Core在频率上的提升只能是缓慢的,而不能够像Pentium 4那样急速上升。 也可以这样猜想,其实Core的流水线设计和P6构架中的流水线是一模一样的,额外多出来的2条流水线完全是为了预留下CPU频率提升的空间而已。2条新的流水线各自成为Core流水线的入口和出口,成为了宏指令融合(Macro-Fusion)、微指令融合(Micro-Ops Fusion)等整合技术的输送站。 Core的内部出口 Core的ROB重排序缓冲区( Reorder Buffer)和RS预留缓存(Reservation Station)要比过去的Pentium M大了接近一倍,而事实上还必须考虑到新的宏指令融合(Macro-Fusion)、微指令融合(Micro-ops Fusion)等高效率的融合技术,这样以来,Core的内部转接速度至少要比Pentium M提高了3倍以上。 Core的处理前站-指令解码 下图为P6构架的指令解码环节,它内置2组SD简单编译器(Simple/fast Decoders)和1组CD复杂编译器(Complex/slow Decoder),2组SD简单编译器负责将简单X86指令转换至Uops微指令(Micro-ops)然后传送到MB微指令缓冲区(Micro-op Buffer)。复杂编译器可以编译4个Uops微指令,而一些类似字符串处理的旧式复杂任务还要通过专门的ME微码引擎(Microcode Engine)来转换为更加复杂的微指令,这些微指令再同时输入到MB微指令缓冲区等待下一步重排序。 对于分支构架比P6宽的多的Core而言这样的旧式微指令处理能力是不够的,所以INTEL在Core中多加入了一组简单编译器(Simple Decoders),并且将MB微指令缓冲区的出口被扩宽至同时传送4条微指令。而更特别的是,过去需要堵塞着等待CD复杂编译器处理的许多内存和SSE数据现在可以由简单编译器来处理了,这都得宜于新的MIF微指令融合技术(Micro-ops Fusion)和改进的SSE,在下文中会详细介绍。 宏指令融合 Core前端处理环节新的突出能力是宏指令融合(Macro-Fusion),可以把多个X86指令融合在一起发送到到一个编译器转换为一个Uops微指令。多种指令将可以被融合,其中特别将compare和test指令融合到了分支指令(Branch Instructions)中。4个编译器都具有融合能力,但整个单元每周期只能完成一次宏指令融合。除了在占用更少ROB和RS的情况下,宏指令融合(Macro-Fusion)还节约了内核前端的带宽,Core的解码单元能比过去快的多得清空IQ指令列队(Instruction Queue),而内核执行带宽也同样宽阔了很多,因为单个的ALU能同时执行2个X86指令,这些综合性能的提高使Core的实际处理效率比P6构架要提高多倍,远高于其可见的硬件单元增加幅度。 微指令融合 MIF微指令融合早先在Pentium M构架上就已经采用过,它和MF宏指令融合有着相似的功效,但是原理完全不一样。SD简单编译器(Simple/fast Decoder)把接收的单条X86指令转译为两条微指令,连接的两条微指令通过ROB发送到RS后,RS将把两条微指令分开来传输到不同的PORT中,平行的双通道同时传输,也可以是单通道的连续传输,这则取决于具体的处理情况。相对旧的MIF微指令融合技术,新的MIF支持了PORT的连续传输。 同宏指令融合技术相结合,Core构架在ROB和RS最大效率的流通更多的微指令、指令执行单元的处理速度和能力也极大提高的同时,反而占用了更少数量的硬件,这符合了Core高效率低功耗的设计原则。 在性能与能耗的平衡决策中,INTEL最终在Core的BP分支预测单元(Branch Predictor)上投入了大量的晶体管。 作为连接内存和CPU的重要环节,在BP分支预测上投入宝贵的晶体管资源是十分值得的。相对于预测错误后让CPU浪费时间和电耗来等待再次预测,一次准确的预测不仅仅节约了处理时间、提高了性能,也同样降低了CPU的功耗。 Core的三重分支预测单元实际上与Pentium M的预测单元是一样的,在Core的分支预测核心中存在一个双模态预测器和一个球型预测器,这些预测器记录下过去的执行历史并随时通知内核前端的ROB和RS,ROB和RS从BTB分支目标缓冲器(Branch Target Buffer)中快速取回所需要的数据地址,常规预测如通知一个分支在循环中仅在奇次迭代发生, 而不在偶次迭代中发生等, 这些在动态执行(P6系列)处理器上的静态预测技术还有有着长远的发展空间。 Core的分支预测单元拥有新的预测器- 循环回路预测(Loop Detector)与间接分支预测(Indirect Branch Predictor)。 循环回路预测 分支历史表(Branch History Tables)不能够记录下足够详细的循环回路历史来准确预测下次的运算,所以每次循环回路的运行都浪费了大量的亢余时间。 循环回路预测(Loop Detector)则可以记录下每个循环回路结束前的所有的详细分支地址,当下一次同样的循环回路程序需要运算时,内核前端的ROB和RS就可以以100%的准确度来快速完成任务,Core构架拥有一个专门的运算法则来进行这种循环回路预测。 间接分支预测 间接分支预测(Indirect Branch Predictor)在运用时并不是立即分支,而是从寄存器中装载需要的预测目标,它实际上是一个首选目标地址的历史记录表。在ROB和RS需要间接分支的时候它就可以提供帮助,ROB和RS就可以快速提取到适用的结果,这与P6构架用可预测的条件分支替换间接分支来改善性能是相反的。 |

| |||||||||||||||||||||||||||||||||||||||||||

| 新浪首页 > 科技时代 > 硬件 > 正文 |

|

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||