|

不支持Flash

|

|

|

|

最后的单核 英特尔新赛扬全系列CPU横测(3)http://www.sina.com.cn 2007年06月12日 11:39 中关村在线

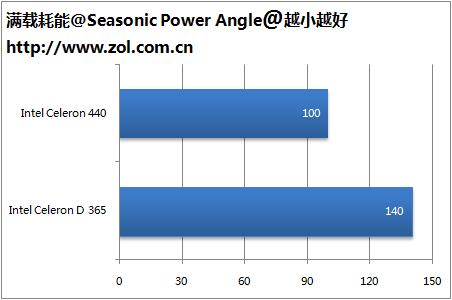

●耗能降低40%,效能如何? 客观而言,基于旧有NetBurst微架构设计的处理器在耗能方面的表现并不尽如人意,因此在Core微架构中,Intel引入了名为“Intelligent Power Capability”的智能耗能管理技术。“Sleep Transistors”休眠晶体管技术能够帮助处理器仅在需要时才开启相应的工作电路,即便是Core 2 Extreme x6800的TDP耗能亦可以被控制在65w的较低水准之上,而Conroe-L核心的Celeron 400系列更是将这一数值拉低至35w。

一方面,Celeron 400系列采用领先的65nm应变硅技术,使用Low-K Dielectric物质并增加金属层,相比于旧有90nm制程产品减少漏电情况达1000倍。另一方面,在Sleep Transistors休眠晶体管技术的作用下,Celeron 400系列处理器内部的各个运算单元均能够独立控制VCC电压,而这些部分在闲置时可被运作于低耗能模式下,使得Celeron 400系列处理器的TDP耗能可以被控制在35w的以内,而其实际运行耗能则能够被控制在20w左右。 当然,在过往的处理器产品中实现Power Gating电源闸控是十分困难的。因为处理器内部元件在开关过程中不仅需要克服能源消耗,还需要克服由休眠恢复至正常工作状态时所造成的延迟。而在Intelligent Power Capability智能耗能管理控制中,Intel对于Sleep Transistors休眠晶体管技术做出了应用性优化,用以保证处理器不会因为局部停止工作而影响效能。

我们分别对Celeron 400系列以及Celeron D系列两代产品中的Celeron 440和Celeron D 365所在的平台进行了耗能测试。在仅更换处理器的前提下,Celeron 440所在的平台总体耗能比Celeron D 365下降了40%之多。

【发表评论】

|

|||||||||||||||