Core2 Extreme X6800与AMD FX62对比测试(2) |

|---|

| http://www.sina.com.cn 2006年06月19日 10:18 PCPOP-电脑时尚 |

|

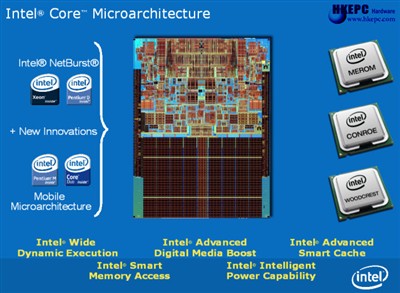

NetBurst + Mobile = Intel Core Microarchitecture !?  Intel Core Microarchitecture

有别于上一代Netburst,Intel Core微架构将会统一用于桌面电脑(Conroe)、行动电脑(Merom)及主流伺服器(WoodCrest)产品中。据Intel表示,Core微架构整合了Mobile架构的省电高效率电表与Netburst优秀功能,并为Multi-Core应用作出准备及优化。话虽如此,但我们却很难在Core微架构中找到半点Netburst的影子,而且它的设计近乎90%是基于Mobile架构的Yonah核心作出改良,而只保留了NetBurst架构中的Prefetching,故此把Core微架构说成把Netburst和Mobile架构结合是有点牵强,或许Intel并不希望外界认为其放弃Netburst架构,名义上让Netburst有更好的台阶下。 虽然Intel Core 微架构是基于Yonah的设计,但其实约有70-80%的架构和线路被重新设计,并加入了五项主要改革,包括Intel Wide Dynamic、Intel Intelligent Power Capability、Intel Adcanced Smart Cache、Intel Smart Memoru Acess及Intel Adcanced Digital Media Boost,而本文亦将会详细介绍这五项改革的原理。 Intel Wide Dynamic Execution  Intel Wide Dynamic Execution

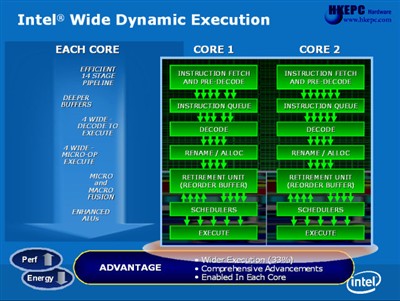

Pentium Pro开始,Intel加入了Dynamic execution动态执行,令x86处理器首次支援Data Flow Analysis、Speculative Execution、Out of Order Execution及Super Scalar等RISC的处理器技术技术。直至Pentium 4的NetBurst架构则被再度改良称为Advanced Dynamic Executive,它采用更深的Out of Order Speculative Executive引擎,以善用高Pipeline Stage架构减少浪费,同时改善Branch-Prediction机制减少造成分支预测错误,全是为了高时脉政策而铺路。

明显地,Intel Core微架构的Wide Dynmaic Execution和Adcanced Dynamic Executive意念不同,它的出发点在于如何提高每周期指令处理数目,改善执行时间及提升处理器的能源效益,Core微架构拥有4组Decoder(3 Simple decoders + 1 Complex decoder),比上代Pentium Pro(P6)/PentiumII/PentiumIII/Pentium M架构拥有2 Simple decoders + 1 Complex decoder可多处理一组指令,与AMD K8不同的是它只拥有3组Complex ecoders,正常来说大部份x86指令均可以采用Simple Coder把它翻译成一个Micro-Op指令,只有极少数学运算的指令,需要采用Complex decoders来把它翻译为四个Micro-Ops指令,因此在正常情况下Core微架构对比Netburst及K8有更优秀的指令执行效率。取消了高时脉政策,Intel Core微架构用回较高效率的14层Pipelines,为了提升分支预测的能力及准确性,Branch Predictor的Bandwitdh提升20B(K8、Banias为16B,Netburst为4B),这些都是体现了"Wide"的意念。  without Macro-Fusion

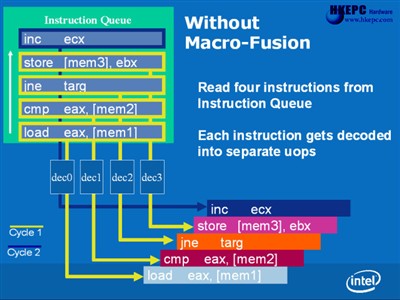

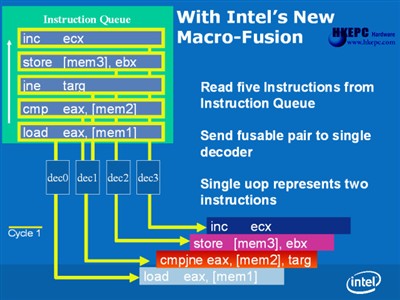

Wide Dynamaic Execution首次加入了Macro-Fusion技术。在旧世代的微架构中,每个指令被送来时其解码及执行动作是完全独立的,但Intel Core微架构可以让常见的指令组例如一个Compare指令配随后拥有一个Jump指令,便可把这个指令组合成单一的Micro-Op指令,这令Core微架构在特定情况下每个周期有运算五组指令,据Intel表示大部份x86程序,约每十至十五个指令就会出现一组可透过Macro -Fusion被组合,因此减少了程序执行所需运算时间、提升效能却不会增加处理器的功耗,为此Intel亦改良ALU(Arithmetic Logic Unit)部份以支援Macro-Fusion技术。  with intel's new Macro-Fusion

此外,Intel Core微架构保留了Banias微架构的Micro-op Fusion技术,在现代的x86处理器,x86指令(Macro-ops)会被分拆去为长短相同的Micro-Ops指令,才会被送往处理器的Pipeline等候执行,而Micro-op Fusion能把相同的Macro-ops混合成单一个Micro-ops,减少了Micro-ops运算的数目亦令处理器运作排序更有效率,据Intel表示,Micro-op Fision透过Out-of-order逻辑可以减高达10%的Micro-op指令执行数。总括而言,Macro-Fusion及Micro-op Fision提升了核心的执行效率同时保持高能源效益。

|

不支持Flash

| 新浪首页 > 科技时代 > 硬件 > 正文 |

|

|

|

| |||||||||||||||||||||||||||||||||||||

|

科技时代意见反馈留言板 电话:010-82628888-5595 欢迎批评指正 新浪简介 | About Sina | 广告服务 | 联系我们 | 招聘信息 | 网站律师 | SINA English | 会员注册 | 产品答疑 Copyright © 1996 - 2006 SINA Inc. All Rights Reserved 新浪公司 版权所有 |