适可而止最重要 详解电脑超频的五大害处(4) |

|---|

| http://www.sina.com.cn 2005年06月21日 14:04 PCPOP-电脑时尚 |

|

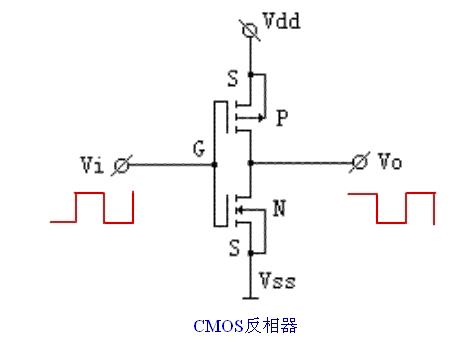

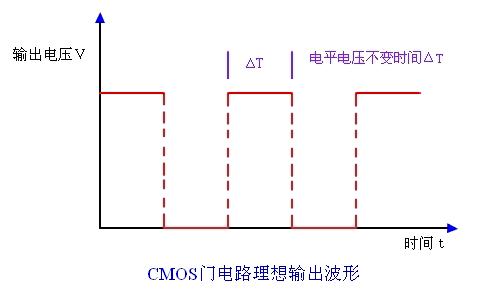

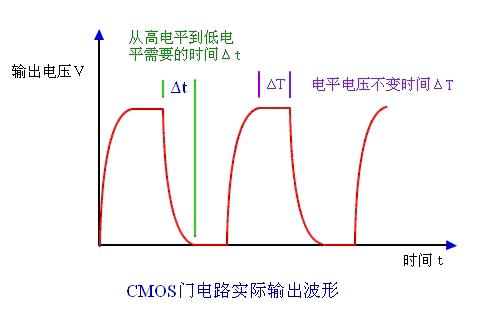

文/醉千千 超频后果三:信号变差 前面说过,CPU是信号处理器,主要功能是对数字信号进行处理,其主要工作单元为由晶体管组成的门电路。下图是CMOS集成电路中的一个最基本电路――反相器,其它复杂的CMOS集成电路大多是由反相器单元组合而成。  CMOS反相器 理论上,CMOS门电路输出的数字信号(也是下一级门电路的输入信号)理想波形的上、下沿都是严格垂直的,从高电平跳变到低电平是突变的,不需要时间。  CMOS门电路理想输出波形 但是,实际上任何实物集成电路最终的性能都不可能完全达到理论指标。CMOS门电路输出波形也不是严格理论上的”方波”,在电压跳变的过程中,不但输出电压不是严格垂直,而且还需要耗费一定的时间。  CMOS门电路实际输出波形 图中的Δt是指从高电平到低电平所需要的时间。这是因为CMOS门电路中几乎无处不在的寄生电容和寄生电阻。而电容器件最重要的一个特性就是,不允许电容器两端的电压突变,而必须有个上升或者下降的过程。只要有寄生电容的存在,Δt的存在就不可避免。通常,寄生电容的主要有以下几种:1)作为输出的晶体管的结电容;2)作为上级负载的下一级输入的晶体管的结电容;3)传输导线之间和晶体管之间的电容。 寄生电阻和寄生电容越小,高低电平的转换时间Δt在整个信号中占据的百分比越小,实际输出的波形也就越接近于理想波形,集成电路的电气性能就更优秀。它们只能通过制造工艺的提高去减小,而不可能完全消失。高k栅介质(High K gate Dielectric)、SOI工艺绝缘体上硅芯片技术(Silicon On Insulator)、“Low-k”低介电常数绝缘体技术等技术都是为了减小CPU中寄生电容采用的方法,而铜互连则有效减小了CPU中寄生电阻。然而不容乐观的是,随着集成密度的提高,线宽越来越窄,导线之间和晶体管之间的距离越来越近,晶体管栅极层厚度越来越薄,这几年CPU寄生电容和电阻的增加已经成为CPU制造技术中最难又最亟待解决的问题。 超频的CPU会使信号波形变的更差。因为CPU成品以后,其电容和电阻值都为常数,晶体管的各项参数也已经固定。在信号电压值不变的情况下, 信号高低电平的跳变所需要的时间也不变。但是频率的提高会使信号宽度 (占用的时间)变短,最终造成波形进一步恶化。

可以看见,超频以后的信号更加“非理想化”,电平电压不变的时间ΔT逐渐减小,给信号的辨认造成困难。当频率增加过高.门电路还未达到最高电平和最低电平的电压要求值就开始“跳变”。波形严重失真,并且可能造成信号达不到下一级门电路的触发电压而使整个CPU无法工作。通常,这种过度超频会造成电脑根本无法启动、黑屏等故障。 |

| 新浪首页 > 科技时代 > 硬件 > 正文 |

|

| |||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||

|

科技时代意见反馈留言板 电话:010-82628888-5828 欢迎批评指正 新浪简介 | About Sina | 广告服务 | 联系我们 | 招聘信息 | 网站律师 | SINA English | 会员注册 | 产品答疑 Copyright © 1996 - 2005 SINA Inc. All Rights Reserved |